플립플롭과 래치

플립플롭(flip-flop)과 래치(latch)는 2개의 안정된(bi-stable) 상태 중 하나를 가지는 1비트 기억 소자이다.

플립플롭과 래치도 게이트로 구성되지만 조합논리회로와 달리 궤환(feed back)이 있다.

NOR 게이트로 구성된 SR 래치

| S | R | Q(t+1) |

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 금지 |

S=0, R=0 일 때: Q(t+1) = Q(t), 출력의 상태가 변하지 않는다.

S=0, R=1 일때: S가 Q로 출력된다.

S=1, R=0 일 때: S가 Q로 출력된다.

S=1, R=1 일 때: Q와 'Q가 반전되지 않으므로 입력이 금지된다.

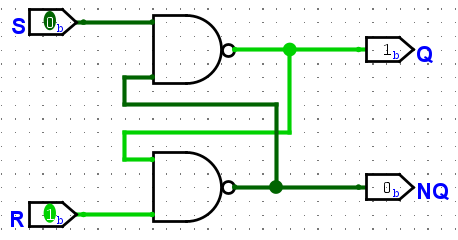

NAND 게이트로 구성된 SR 래치

| S | R | Q(t+1) |

| 0 | 0 | 금지 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | Q(t) |

S=0, R=0 일 때: Q와 'Q가 반전되지 않으므로 입력이 금지된다.

S=0, R=1 일 때: R이 Q로 출력된다.

S=1, R=0 일 때: R이 Q로 출력된다.

S=1, R=1 일 때: Q(t+1) = Q(t), 출력의 상태가 변하지 않는다.

'논리회로' 카테고리의 다른 글

| 그레이 코드 변환 & 패리티 발생기·검출기 완전 정리 (0) | 2025.05.11 |

|---|---|

| 멀티플렉서 완전 정리: 2×1부터 16×1 구성까지 한눈에 이해하기 (0) | 2025.05.11 |

| 인코더(Encoder) 정리: 2×1, 4×2 구조와 논리식까지 한눈에 이해하기 (0) | 2025.05.11 |

| 디코더와 디멀티플렉서 : 1×2, 2×4 구조와 논리식까지 (0) | 2025.05.11 |

| 비교기(Comparator) 완전 정리: 1비트부터 4비트까지 크기 비교 회로 이해하기 (0) | 2025.05.11 |